DynaPlasia: Reconfigurable Spatial Accelerator with eDRAM-IMC

본문

Overview

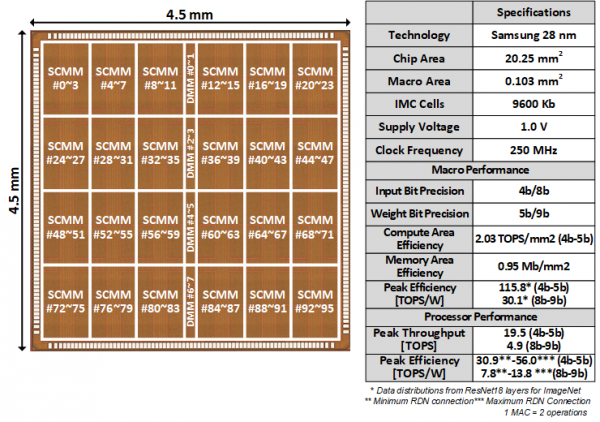

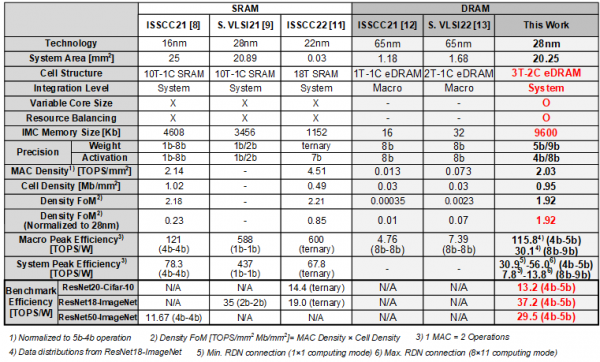

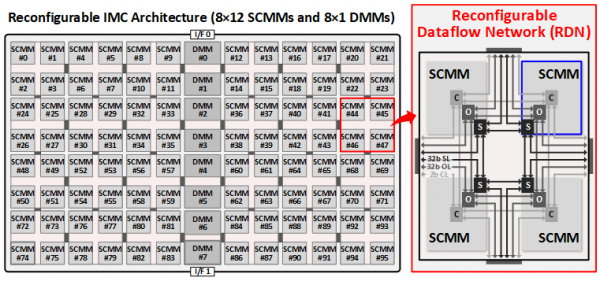

We present an eDRAM-based CIM processor called DynaPlasia with a novel triple-mode 3T2C cell and a dynamic reconfigurable core architecture that enables high system efficiency for ML workloads. For ResNet-18 (ImageNet dataset), DynaPlasia achieves system energy efficiency of 37.2TOPS/W and compute density of 2.03TOPS/mm2 at 1.0V and 250MHz for INT4/INT5 activation/weight precision

Features

- Dynamic Reconfigurable Core Architecture

- Triple-mode Cell

- Hierarchical In-memory ADC

- Signed-input Signed-weight IMC Operation

- Leakage Tolerant Computing

Related Papers

- ISSCC 2023