2024

IRIS

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm Logic CMOS 4.5 mm × 4.5 mm 0.7 ~ 0.9 V Real-time 3D Rendering Accelerator Maximum : 200 MHz 584 mW Aug. 2024

|

2024

IRIS

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm Logic CMOS 4.5 mm × 4.5 mm 0.7 ~ 0.9 V Real-time 3D Rendering Accelerator Maximum : 200 MHz 584 mW Aug. 2024 |

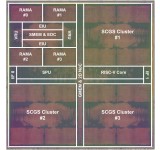

2024

BROCA

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm LPP 4.5 mm × 4.5 mm 0.7 ~1.1 V Mobile social agent SoC Maximum: 200 MHz 52.4 mW (@ 50MHz, 0.7V), 559.2 mW (@ 200MHz, 1.1V) Aug. 2024

|

2024

BROCA

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm LPP 4.5 mm × 4.5 mm 0.7 ~1.1 V Mobile social agent SoC Maximum: 200 MHz 52.4 mW (@ 50MHz, 0.7V), 559.2 mW (@ 200MHz, 1.1V) Aug. 2024

|

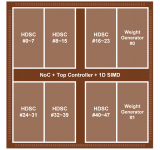

2024

EdgeDiff

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS 4.5 mm × 4.5 mm 0.68 ~ 1.0 V Efficient few-step diffusion acceleration 50 ~ 250 MHz Generation Energy 418.4 mJ/Inference Aug. 2024

|

2024

EdgeDiff

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS 4.5 mm × 4.5 mm 0.68 ~ 1.0 V Efficient few-step diffusion acceleration 50 ~ 250 MHz Generation Energy 418.4 mJ/Inference Aug. 2024 |

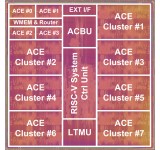

2024

Slim-Llama

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS 4.5 mm × 4.5 mm 0.7 ~ 0.9 V Ultra-low-power LLM acceleration 25 ~ 200 MHz 4.69 mW (@ 25MHz, 0.58V), 82.07 mW (@ 200MHz, 1.0V) Aug. 2024

|

2024

Slim-Llama

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS 4.5 mm × 4.5 mm 0.7 ~ 0.9 V Ultra-low-power LLM acceleration 25 ~ 200 MHz 4.69 mW (@ 25MHz, 0.58V), 82.07 mW (@ 200MHz, 1.0V) Aug. 2024 |

2023

Space-Mate

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.7V ~ 0.9V Neural rendering-based SLAM processor Maximum: 200MHz 114.1 ~ 623.4 mW Aug. 2023

|

2023

Space-Mate

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.7V ~ 0.9V Neural rendering-based SLAM processor Maximum: 200MHz 114.1 ~ 623.4 mW Aug. 2023 |

2023

C-Transformer

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.7V ~ 1.1V Complementary DNN-Transformer / Spiking-Transformer Processor Maximum: 200MHz 47.5mW ~ 469.2mW Aug. 2023

|

2023

C-Transformer

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.7V ~ 1.1V Complementary DNN-Transformer / Spiking-Transformer Processor Maximum: 200MHz 47.5mW ~ 469.2mW Aug. 2023 |

2023

NeuGPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.68V ~ 0.9V Neural Graphics Processing Unit Maximum: 200MHz Modeling: 559.5 mW / Rendering: 728.4 mW

Aug. 2023

|

2023

NeuGPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.68V ~ 0.9V Neural Graphics Processing Unit Maximum: 200MHz Modeling: 559.5 mW / Rendering: 728.4 mW

Aug. 2023 |

2022

C-DNN

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.7V ~ 1.1V Complementary DNN Processor Maximum: 200MHz ~40mW Aug. 2022

|

2022

C-DNN

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.7V ~ 1.1V Complementary DNN Processor Maximum: 200MHz ~40mW Aug. 2022 |

2022

MetaVRain

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.6V ~ 0.95V NeRF-based 3D Neural Rendering Processor 50MHz ~ 250MHz 133mW ~ 899mW Aug. 2022

|

2022

MetaVRain

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28 nm 1P8M CMOS Process

4.5mm × 4.5mm 0.6V ~ 0.95V NeRF-based 3D Neural Rendering Processor 50MHz ~ 250MHz 133mW ~ 899mW Aug. 2022 |

2022

DynaPlasia

Technology

Chip Size

Function

PIM Cells Peak Throughput

Released Date

Samsung 28nm 1P8M CMOS Process

4.5mm × 4.5mm eDRAM IMC-based Mobile DNN Inference 9600Kb 19.5 TOPS (4b-5b) Aug. 2022

|

2022

DynaPlasia

|

Technology

Chip Size

Function

PIM Cells Peak Throughput

Released Date |

Samsung 28nm 1P8M CMOS Process

4.5mm × 4.5mm eDRAM IMC-based Mobile DNN Inference 9600Kb 19.5 TOPS (4b-5b) Aug. 2022

|

2021

DSPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28nm 1P8M CMOS Process 3.6mm x 3.6mm 0.72V ~ 1.1V 3D Object Recognition Processor Maximum: 250MHz 440mW Jul. 2021

|

2021

DSPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28nm 1P8M CMOS Process 3.6mm x 3.6mm 0.72V ~ 1.1V 3D Object Recognition Processor Maximum: 250MHz 440mW Jul. 2021 |

2021

Neuro-CIM

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28nm 1P8M CMOS Process 3.2mm x 0.9mm 1.1V Neuromorphic Network Acceleration in Mobile Devices Maximum: 200MHz 105.44mW ~ 241.44mW Jun. 2021

|

2021

Neuro-CIM

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28nm 1P8M CMOS Process 3.2mm x 0.9mm 1.1V Neuromorphic Network Acceleration in Mobile Devices Maximum: 200MHz 105.44mW ~ 241.44mW Jun. 2021 |

2021

SNPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28nm 1P8M CMOS Process 3.2mm x 1.9mm 0.63V ~ 1.1V Spike-Neural-Network Acceleration in Mobile Devices Maximum: 200MHz 0.31mW ~ 186.84mW Jun. 2021

|

2021

SNPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28nm 1P8M CMOS Process 3.2mm x 1.9mm 0.63V ~ 1.1V Spike-Neural-Network Acceleration in Mobile Devices Maximum: 200MHz 0.31mW ~ 186.84mW Jun. 2021 |

2020

PNNPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process 4mm x 4mm 0.78V ~ 1.1V Mobile Intelligent 3D Vision NPU 50MHz ~ 200MHz 331mW Aug. 2020

|

2020

PNNPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process 4mm x 4mm 0.78V ~ 1.1V Mobile Intelligent 3D Vision NPU 50MHz ~ 200MHz 331mW Aug. 2020 |

2020

HNPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28nm 1P8M CMOS Process

3.6 mm x 3.6 mm 0.58~1.04V Mobile DNN Inference & Training + Privacy-preserving Cloud-edge Co-training Maximum: 250 MHz 1.95 mW ~ 1162 mW Jul. 2020

|

2020

HNPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28nm 1P8M CMOS Process

3.6 mm x 3.6 mm 0.58~1.04V Mobile DNN Inference & Training + Privacy-preserving Cloud-edge Co-training Maximum: 250 MHz 1.95 mW ~ 1162 mW Jul. 2020

|

2020

OmniDRL

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

28nm CMOS Process

3.6 mm x 3.6 mm 0.68V ~ 1.1 V Deep Reinforcement Learning ~250 MHz 3.1 mW ~ 282.8 mW (Peak) Aug. 2020

|

2020

OmniDRL

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

28nm CMOS Process

3.6 mm x 3.6 mm 0.68V ~ 1.1 V Deep Reinforcement Learning ~250 MHz 3.1 mW ~ 282.8 mW (Peak) Aug. 2020

|

2020

MAC

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

Samsung 28nm FDSOI

2.7mm x 2.7mm

0.3 ~ 1V (Analog), 1V (Digital)

ECG Arrhythmia detection 1kHz ~ 30kHz (Analog), 100MHz (Digital)

1uW

Jan. 2020

|

2020

MAC

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

Samsung 28nm FDSOI

2.7mm x 2.7mm

0.3 ~ 1V (Analog), 1V (Digital)

ECG Arrhythmia detection 1kHz ~ 30kHz (Analog), 100MHz (Digital)

1uW

Jan. 2020 |

2019

EIT

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process

4.0 mm x 4.0 mm 3.3 V (Analog), 1.8V (Digital) Electrical Impedance Tomography 10 kHz ~ 10 MHz 9.6 mW/Ch

July. 2019

|

2019

EIT

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4.0 mm x 4.0 mm 3.3 V (Analog), 1.8V (Digital) Electrical Impedance Tomography 10 kHz ~ 10 MHz 9.6 mW/Ch

July. 2019

|

2019

GANPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

65 nm 1P8M CMOS Process 8.1 mm x 4.0 mm 0.70 V ~ 1.1 V Generative Adversarial Network Inference & Training Maximum 200 MHz Maximum 647 mW Jul. 2019

|

2019

GANPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

65 nm 1P8M CMOS Process 8.1 mm x 4.0 mm 0.70 V ~ 1.1 V Generative Adversarial Network Inference & Training Maximum 200 MHz Maximum 647 mW Jul. 2019

|

2018

LNPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

0.78V ~ 1.1V

DNN Learning 50MHz ~ 200MHz

43.1mW ~ 367mW(Peak)

Jul. 2018

|

2018

LNPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

0.78V ~ 1.1V

DNN Learning 50MHz ~ 200MHz

43.1mW ~ 367mW(Peak)

Jul. 2018 |

2018

IOT

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date

180nm High Voltage CMOS Process

3.3mm x 5mm

1.8V for Supply, 7V for LED

Optical and Electrical Dual Tomographic Imaging

7.6mW for Average

Aug. 2018

|

2018

IOT

|

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date |

180nm High Voltage CMOS Process

3.3mm x 5mm

1.8V for Supply, 7V for LED

Optical and Electrical Dual Tomographic Imaging

7.6mW for Average

Aug. 2018 |

2018

ICE

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date

180nm 1P6M CMOS Process

2.35mm x 5.0mm

1.5V

Intracardiac Echocardiography

TX: 3.31mW(5Vpp), 9.26mW(13.2Vpp), RX: 0.95mW

Jul. 2018

|

2018

ICE

|

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date |

180nm 1P6M CMOS Process

2.35mm x 5.0mm

1.5V

Intracardiac Echocardiography

TX: 3.31mW(5Vpp), 9.26mW(13.2Vpp), RX: 0.95mW

Jul. 2018 |

2018

GLY

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption Resolution Phase Error

Released Date

65nm 1P8M CMOS Process

3.55mm x 1.36mm

0.5V

Bio-Impedance Sensor 20kHz ~ 50kHz

9.26μW 15.28mΩ/√Hz <0.55°

Jul. 2018

|

2018

GLY

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption Resolution Phase Error

Released Date |

65nm 1P8M CMOS Process

3.55mm x 1.36mm

0.5V

Bio-Impedance Sensor 20kHz ~ 50kHz

9.26μW 15.28mΩ/√Hz <0.55°

Jul. 2018 |

2018

CNPU

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

0.67V ~ 1.1V

Mobile Deep Reinforcement Learning 10MHz ~ 200MHz

2.4mW ~ 196mW(Peak)

Jul. 2018

|

2018

CNPU

|

Technology

Chip Size

Power Supply

Function Operating Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

0.67V ~ 1.1V

Mobile Deep Reinforcement Learning 10MHz ~ 200MHz

2.4mW ~ 196mW(Peak)

Jul. 2018 |

2017

BASE

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

1.0V, 3.0V

Body Channel Communication

TX: 0.8mW ~ 1.7mW (Peak) / RX: 8mW

Aug. 2017

|

2017

BASE

|

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

1.0V, 3.0V

Body Channel Communication

TX: 0.8mW ~ 1.7mW (Peak) / RX: 8mW

Aug. 2017 |

2017

CSP

Technology

Chip Size

Power Supply

Function

Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

0.9V ~ 1.2V

Convolutional Neural Network

10MHz ~ 100MHz

9.02mW ~ 31.20mW (Peak)

Aug. 2017

|

2017

CSP

|

Technology

Chip Size

Power Supply

Function

Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

0.9V ~ 1.2V

Convolutional Neural Network

10MHz ~ 100MHz

9.02mW ~ 31.20mW (Peak)

Aug. 2017 |

2017

UNPU

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

0.63 ~ 1.1V

Deep Neural Network

5MHz ~ 200MHz

3.2mW ~ 297mW (Peak)

Aug. 2017

|

2017

UNPU

|

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

0.63 ~ 1.1V

Deep Neural Network

5MHz ~ 200MHz

3.2mW ~ 297mW (Peak)

Aug. 2017 |

2016

ANES

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

1.2V, 3.3V

EEG + NIRS Anesthesia Monitoring

25.2mW (Peak)

Jul. 2016

|

2016

ANES

|

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

1.2V, 3.3V

EEG + NIRS Anesthesia Monitoring

25.2mW (Peak)

Jul. 2016 |

2016

CNNP

Technology

Chip Size

Power Supply

Function

Frequency

Power Consumption

Released Date

65nm 1P8M CMOS Process

4mm x 4mm

0.46V ~ 1.0V

Convolutional Neural Network

5MHz ~ 100MHz

5.3mW ~ 211mW (Peak)

Aug. 2016

|

2016

CNNP

|

Technology

Chip Size

Power Supply

Function

Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS Process

4mm x 4mm

0.46V ~ 1.0V

Convolutional Neural Network

5MHz ~ 100MHz

5.3mW ~ 211mW (Peak)

Aug. 2016 |

2016

FIS

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date

65nm Triple-Well CMOS Technology

3.3mm x 3.36mm

2.5V (Pixel), 0.5V ~ 1.2V (Other)

Face Detection (Viola Jones)

7MHz ~ 245MHz

24μW (Avg.)

Aug. 2016

|

2016

FIS

|

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date |

65nm Triple-Well CMOS Technology

3.3mm x 3.36mm

2.5V (Pixel), 0.5V ~ 1.2V (Other)

Face Detection (Viola Jones)

7MHz ~ 245MHz

24μW (Avg.)

Aug. 2016 |

2016

DNPU

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date

65nm 1P8M CMOS

4mm x 4mm (16㎟)

0.77V ~1.1VV

General Purpose Deep Neural-network Processor

50MHz ~ 200MHz

34.6mW (50MHz @0.77V), 279mW (200MHz @1.1V)

Aug. 2016

|

2016

DNPU

|

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date |

65nm 1P8M CMOS

4mm x 4mm (16㎟)

0.77V ~1.1VV

General Purpose Deep Neural-network Processor

50MHz ~ 200MHz

34.6mW (50MHz @0.77V), 279mW (200MHz @1.1V)

Aug. 2016 |

2016

WIT

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date

65nm Triple-Well CMOS Technology

Sensor: 1.1mm x 2.9mm, Hub: 1.4mm x 0.9mm

1.2V

3D Lung Electrical Impedance Tomography

6.96mW

Aug. 2016

|

2016

WIT

|

Technology

Chip Size

Power Supply

Function

Power Consumption

Released Date |

65nm Triple-Well CMOS Technology

Sensor: 1.1mm x 2.9mm, Hub: 1.4mm x 0.9mm

1.2V

3D Lung Electrical Impedance Tomography

6.96mW

Aug. 2016 |

2015

BRAIN

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date

65nm Triple-Well CMOS Technology

4mm x 4mm

0.55V ~ 1.2V

Ultra-Low-Power Robot AI Processor

(Tree Search + Reinforcement Learning)

7MHz ~ 245MHz

1.1mW ~ 151mW

Jul. 2015

|

2015

BRAIN

|

Technology

Chip Size

Power Supply

Function

Operating Frequency

Power Consumption

Released Date |

65nm Triple-Well CMOS Technology

4mm x 4mm

0.55V ~ 1.2V

Ultra-Low-Power Robot AI Processor

(Tree Search + Reinforcement Learning)

7MHz ~ 245MHz

1.1mW ~ 151mW

Jul. 2015 |

2015

AutoBrain

Technology

Chip Size

Power Supply

Function

Operating Frequency

Peak performance Power Consumption

power efficiency

energy efficiency

Released Date

65nm 1P8M CMOS Process

4.0mm x 4.0mm

1.2V (Nominal), 0.65V~1.2V (DVFS)

Intelligent ADAS & Real-time SGM

250MHz (Nominal), 50MHz~250MHz (DVFS)

502GOPS

330mW (avg.), 582mW (peak)

862GOPS/W

31.4GOPS/mm2

July 2015

|

2015

AutoBrain

|

Technology

Chip Size

Power Supply

Function

Operating Frequency

Peak performance Power Consumption

power efficiency

energy efficiency

Released Date |

65nm 1P8M CMOS Process

4.0mm x 4.0mm

1.2V (Nominal), 0.65V~1.2V (DVFS)

Intelligent ADAS & Real-time SGM

250MHz (Nominal), 50MHz~250MHz (DVFS)

502GOPS

330mW (avg.), 582mW (peak)

862GOPS/W

31.4GOPS/mm2

July 2015 |

2015

MoST

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date

0.18 μm 1P6M CMOS Process

2.35 mm x 5.0 mm

1.5V, 5V

Sticker-type SpO2 / ExG Monitoring System

OLED Driver, OPD Sensor Front-end, Optical Calibration Loop, Clock Broadcasting TRx

141μW ~ 1300μW

Aug. 2015

|

2015

MoST

|

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date |

0.18 μm 1P6M CMOS Process

2.35 mm x 5.0 mm

1.5V, 5V

Sticker-type SpO2 / ExG Monitoring System

OLED Driver, OPD Sensor Front-end, Optical Calibration Loop, Clock Broadcasting TRx

141μW ~ 1300μW

Aug. 2015 |

2015

NINE-X

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date

65 nm 1P8M CMOS Process

4.0 mm x 4.0 mm

0.5~1.2V

Natural User Interface & Experience for HMD

DLE, DIE, TRNG, SSC, HSC, GRE

126.1mW

Aug. 2015

|

2015

NINE-X

|

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date |

65 nm 1P8M CMOS Process

4.0 mm x 4.0 mm

0.5~1.2V

Natural User Interface & Experience for HMD

DLE, DIE, TRNG, SSC, HSC, GRE

126.1mW

Aug. 2015 |

2014

EEG-Connectome Chip

Technology

Chip Size

Power Supply

Function

Channel Frequency

Power Consumption

Released Date

0.18 μm CMOS Process

1.0 mm x 3.8 mm

1.8V

EEG-Connectome Processing

20MHz

1.71mW

Dec. 2014

|

2014

EEG-Connectome Chip

|

Technology

Chip Size

Power Supply

Function

Channel Frequency

Power Consumption

Released Date |

0.18 μm CMOS Process

1.0 mm x 3.8 mm

1.8V

EEG-Connectome Processing

20MHz

1.71mW

Dec. 2014 |

2014

BONE-AR

Technology

Chip Size

Power Supply

Function

Injection Method

Injectable Current

Frame Rate

Power Consumption

Released Date

0.18 μm 1P6M CMOS Technology

2.5 mm x 3.8 mm (including pads)

1.5 V

Electrical Impedance Tomography (EIT)

Dual Frequency Division Multiplexing

125-500μAp-p (10~360kHz)

30fps

4.84mW

Dec. 2014

|

2014

BONE-AR

|

Technology

Chip Size

Power Supply

Function

Injection Method

Injectable Current

Frame Rate

Power Consumption

Released Date |

0.18 μm 1P6M CMOS Technology

2.5 mm x 3.8 mm (including pads)

1.5 V

Electrical Impedance Tomography (EIT)

Dual Frequency Division Multiplexing

125-500μAp-p (10~360kHz)

30fps

4.84mW

Dec. 2014 |

2014

M3H

Technology

Chip Size

Power Supply

Function

Key Accelerators

Power Consumption

Released Date

0.11 μm Dongbu CMOS Process

3.375 mm x 2.25 mm

1.2V, 3.3V

Multimodal Mental Management System IC

Electroencephalography sensor, Near-infrared Spectroscopy sensor

24mW @ maximum condition

Aug. 2014

|

2014

M3H

|

Technology

Chip Size

Power Supply

Function

Key Accelerators

Power Consumption

Released Date |

0.11 μm Dongbu CMOS Process

3.375 mm x 2.25 mm

1.2V, 3.3V

Multimodal Mental Management System IC

Electroencephalography sensor, Near-infrared Spectroscopy sensor

24mW @ maximum condition

Aug. 2014 |

2014

DMLP

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date

65 nm 1P8M CMOS Process

2.5 mm x 4.0 mm

1.2V

Deep Learning and Inference

DLE, DIE, TRNG

185.3mW

Aug. 2014

|

2014

DMLP

|

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date |

65 nm 1P8M CMOS Process

2.5 mm x 4.0 mm

1.2V

Deep Learning and Inference

DLE, DIE, TRNG

185.3mW

Aug. 2014 |

2014

Biocle A

Technology

Chip Size

Power Supply

Function

Modulation

Channel Frequency

Sensitivity

Power Consumption

Released Date

65nm CMOS Technology

1.8 mm x 3.2 mm

1.2V

Body Channel Communication Transceiver

BPSK, OOK

40MHz(40MHz BW), 160MHz(40MHz BW), 13.56MHz(100kHz BW)

-58dBm @ 80Mb/s, -72dBm @ 100kb/s

79pJ/b, 42.5μW

Aug. 2014

|

2014

Biocle A

|

Technology

Chip Size

Power Supply

Function

Modulation

Channel Frequency

Sensitivity

Power Consumption

Released Date |

65nm CMOS Technology

1.8 mm x 3.2 mm

1.2V

Body Channel Communication Transceiver

BPSK, OOK

40MHz(40MHz BW), 160MHz(40MHz BW), 13.56MHz(100kHz BW)

-58dBm @ 80Mb/s, -72dBm @ 100kb/s

79pJ/b, 42.5μW

Aug. 2014 |

2014

NT-FMP

Technology

Chip Size

Function Supply Voltage

Power Consumption

Operating Frequency Released Date

65 nm CMOS Process

4 mm x 0.5 mm

Ultra-low-power Object Matching Processor

0.5V(Logic), 0.8V(SRAM)

54μW

5MHz

|

2014

NT-FMP

|

Technology

Chip Size

Function Supply Voltage

Power Consumption

Operating Frequency Released Date |

65 nm CMOS Process

4 mm x 0.5 mm

Ultra-low-power Object Matching Processor

0.5V(Logic), 0.8V(SRAM)

54μW

5MHz

|

2014

Gaze Image Sensor (GIS)

Technology

Chip Size

Power Supply

Function

Frequency

Peak Performance

Power Consumption

Released Date

65 nm 1P8M CMOS Process

3.36 mm x 3.36 mm

2.5V (Pixel), 1.2V (Other)

Gaze Image Sensor

50MHz

0.3 GOPS

10mW(Average), 34mW(Peak)

Jun. 2014

|

2014

Gaze Image Sensor (GIS)

|

Technology

Chip Size

Power Supply

Function

Frequency

Peak Performance

Power Consumption

Released Date |

65 nm 1P8M CMOS Process

3.36 mm x 3.36 mm

2.5V (Pixel), 1.2V (Other)

Gaze Image Sensor

50MHz

0.3 GOPS

10mW(Average), 34mW(Peak)

Jun. 2014 |

2014

Object Recognition Processor (ORP)

Technology

Chip Size

Power Supply

Function

Frequency

Peak Performance

Power Consumption

Released Date

65 nm 1P8M CMOS Process

4.0 mm x 4.0 mm

1.2V (Normal), 0.7V~1.2V(DVFS)

Object Recognition

50MHz(DGP), 100MHz(FDP/SSP/FMP),

200MHz(CNNP/DRMP/EOGP/FA/NoC)

151 GOPS

65mW(Average), 97mW(Peak)

Jun. 2014

|

2014

Object Recognition Processor (ORP)

|

Technology

Chip Size

Power Supply

Function

Frequency

Peak Performance

Power Consumption

Released Date |

65 nm 1P8M CMOS Process

4.0 mm x 4.0 mm

1.2V (Normal), 0.7V~1.2V(DVFS)

Object Recognition

50MHz(DGP), 100MHz(FDP/SSP/FMP),

200MHz(CNNP/DRMP/EOGP/FA/NoC)

151 GOPS

65mW(Average), 97mW(Peak)

Jun. 2014 |

2013

MSM

Technology

Chip Size

Power Supply

Function

Key Accelerators

Power Consumption

Released Date

0.13 μm 1P8M CMOS Process

2.35 mm x 5.0 mm

3.3V(IO), 0.7-1.0V(Core)

EEG Signal Processing, Transcranial Electrical Stimulation

Independent Component Analysis (ICA), Fast Fourier Transform (FFT),

Support Vector Machine (SVM)

4.45mW

Aug. 2013

|

2013

MSM

|

Technology

Chip Size

Power Supply

Function

Key Accelerators

Power Consumption

Released Date |

0.13 μm 1P8M CMOS Process

2.35 mm x 5.0 mm

3.3V(IO), 0.7-1.0V(Core)

EEG Signal Processing, Transcranial Electrical Stimulation

Independent Component Analysis (ICA), Fast Fourier Transform (FFT),

Support Vector Machine (SVM)

4.45mW

Aug. 2013 |

2013

Gluco Scope2

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date

0.18um 1P6M CMOS Process

2.5 mm x 5.0 mm (including pads)

1.5V

Non-invasive Blood Glucose Level Estimation

Impedance Spectroscopy Circuit,

Multi-wavelength Near-infrared Spectroscopy Circuit

Maximum 38mW

Aug. 2013

|

2013

Gluco Scope2

|

Technology

Chip Size

Power Supply

Function

Key Block

Power Consumption

Released Date |

0.18um 1P6M CMOS Process

2.5 mm x 5.0 mm (including pads)

1.5V

Non-invasive Blood Glucose Level Estimation

Impedance Spectroscopy Circuit,

Multi-wavelength Near-infrared Spectroscopy Circuit

Maximum 38mW

Aug. 2013 |

2013

Biocle5

Technology

Chip Size

Power Supply

Function

Modulation

Channel Frequency

Sensitivity

Power Consumption

Released Date

0.13 μm CMOS Technology

2.5 mm x 5.0 mm

1.2 V

Human Body Communication (HBC) Network Coordinator

Frequency Selective Digital Transmission (FSDT)

21 MHz (5.25 MHz Bandwidth)

-98 dBm @ 124 kbps

33 μW/nodes

Aug. 2013

|

2013

Biocle5

|

Technology

Chip Size

Power Supply

Function

Modulation

Channel Frequency

Sensitivity

Power Consumption

Released Date |

0.13 μm CMOS Technology

2.5 mm x 5.0 mm

1.2 V

Human Body Communication (HBC) Network Coordinator

Frequency Selective Digital Transmission (FSDT)

21 MHz (5.25 MHz Bandwidth)

-98 dBm @ 124 kbps

33 μW/nodes

Aug. 2013 |

2013

SEIT

Technology

Chip Size

Power supply

Function

Sensitivity

Injectable Current

THD

Power Consumption

Released Date

0.18 μm 1P6M CMOS Technology

2.5 mm x 5.0 mm

1.8 V

Electrical Impedance Tomography (EIT)

4.9 mΩ

10-400 μAp-p (0.1-100 kHz)

0.2% @ 200 μAp-p

53.4 mW (USB Supply)

Aug. 2013

|

2013

SEIT

|

Technology

Chip Size

Power supply

Function

Sensitivity

Injectable Current

THD

Power Consumption

Released Date |

0.18 μm 1P6M CMOS Technology

2.5 mm x 5.0 mm

1.8 V

Electrical Impedance Tomography (EIT)

4.9 mΩ

10-400 μAp-p (0.1-100 kHz)

0.2% @ 200 μAp-p

53.4 mW (USB Supply)

Aug. 2013 |

2013

BONE-AR

Technology

Chip Size

Function

Frequency(Nominal)

Peak Performance

Power Dissipation

Area Efficiency

Power Efficiency

Per-frame Energy

Released Date

65nm 1P8M CMOS Process

4.0 mm x 8.0 mm

Markerless Augmented Reality

250 MHz (Digital)

1.22 TOPS

381 mW

38.13 GOPS/mm2

1.57 TOPS/W

12.70 mJ/frame

Jun. 2013

|

2013

BONE-AR

|

Technology

Chip Size

Function

Frequency(Nominal)

Peak Performance

Power Dissipation

Area Efficiency

Power Efficiency

Per-frame Energy

Released Date |

65nm 1P8M CMOS Process

4.0 mm x 8.0 mm

Markerless Augmented Reality

250 MHz (Digital)

1.22 TOPS

381 mW

38.13 GOPS/mm2

1.57 TOPS/W

12.70 mJ/frame

Jun. 2013 |

2012

BONE-V6

Technology

Chip Size

Function

Frequency(Nominal)

Peak Performance

Power Dissipation

Area Efficiency

Power Efficiency

Per-pixel Efficiency

Released Date

0.13 μm 1P8M Mixed-mode CMOS Process

5.0 mm x 5.0 mm

Context-Aware Object Recognition

200 MHz (Digital)

271.4 GOPS

260 mW

10.86 GOPS/mm2

646 GOPS/W

9.4 nJ/Pixel

Aug. 2012

|

2012

BONE-V6

|

Technology

Chip Size

Function

Frequency(Nominal)

Peak Performance

Power Dissipation

Area Efficiency

Power Efficiency

Per-pixel Efficiency

Released Date |

0.13 μm 1P8M Mixed-mode CMOS Process

5.0 mm x 5.0 mm

Context-Aware Object Recognition

200 MHz (Digital)

271.4 GOPS

260 mW

10.86 GOPS/mm2

646 GOPS/W

9.4 nJ/Pixel

Aug. 2012 |

2012

BONE-V5s

Technology

Chip Size

Application

Operating Frequency

Power Consumption

Released Date

65nm 1P8M Logic CMOS

4.0 mm x 4.0 mm

30 fps Object Recognition @ 720p

50–200 MHz

235 mW

Jan. 2012

|

2012

BONE-V5s

|

Technology

Chip Size

Application

Operating Frequency

Power Consumption

Released Date |

65nm 1P8M Logic CMOS

4.0 mm x 4.0 mm

30 fps Object Recognition @ 720p

50–200 MHz

235 mW

Jan. 2012 |

2012

NFC2

Technology

Chip Size

Function

Modulation

Comm. Distance

Speed

Energy

Released Date

0.13 μm 1P6M CMOS Process

2.35 mm x 2.35 mm

mm-range Inductive Coupling Transceiver

Mono-phase Pulse Modulation

>1mm

1.2Gb/s

3.9pJ/b

Aug. 2012

|

2012

NFC2

|

Technology

Chip Size

Function

Modulation

Comm. Distance

Speed

Energy

Released Date |

0.13 μm 1P6M CMOS Process

2.35 mm x 2.35 mm

mm-range Inductive Coupling Transceiver

Mono-phase Pulse Modulation

>1mm

1.2Gb/s

3.9pJ/b

Aug. 2012 |

2012

Smart Ionto

Technology

Chip Size

Power Supply

Function

Life Time

Stimulation Current

Bio-Feedback

Power Consumption

Released Date

0.11 μm 1P6M CMOS Process

2.5 mm x 2.5 mm (including pads)

1.2V

Bio-Feedback Transdermal Drug Delivery

> 3 hours

16-512μA

Load/Tissue Impedance, Skin Temperature

2.2mW

Aug. 2012

|

2012

Smart Ionto

|

Technology

Chip Size

Power Supply

Function

Life Time

Stimulation Current

Bio-Feedback

Power Consumption

Released Date |

0.11 μm 1P6M CMOS Process

2.5 mm x 2.5 mm (including pads)

1.2V

Bio-Feedback Transdermal Drug Delivery

> 3 hours

16-512μA

Load/Tissue Impedance, Skin Temperature

2.2mW

Aug. 2012 |

2012

MSEA

Technology

Chip Size

Function

Modulation

Operating Frequency

Bandwidth

Sensitivity

Power Consumption

Released Date

UMC 0.13 μm CMOS Technology

2.5mm x 5.0 mm (including pads)

IEEE 802.15.6 Standard Compatible Transceiver

FSDT

21MHz

5.25MHz

-97.35dBm

3.2mW(RX), 2.0mW(TX)

Aug. 2012

|

2012

MSEA

|

Technology

Chip Size

Function

Modulation

Operating Frequency

Bandwidth

Sensitivity

Power Consumption

Released Date |

UMC 0.13 μm CMOS Technology

2.5mm x 5.0 mm (including pads)

IEEE 802.15.6 Standard Compatible Transceiver

FSDT

21MHz

5.25MHz

-97.35dBm

3.2mW(RX), 2.0mW(TX)

Aug. 2012 |

2011

IRIS

Technology

Chip Size

Function

Nominal Frequency

Peak Performance

Power Consumption

Per-frame Efficiency

Per-pixel Efficiency

Released Date

0.13 μm 1-P 6-M Logic CMOS Technology

4.0 mm x 8.0 mm

Object Recognition

200MHz @1.2V (Digital)

342 GOPS

534mW (Peak) / 320mW (Ave.)

9.6mJ/Frame

10.5nJ/Pixel

Aug. 2011

|

2011

IRIS

|

Technology

Chip Size

Function

Nominal Frequency

Peak Performance

Power Consumption

Per-frame Efficiency

Per-pixel Efficiency

Released Date |

0.13 μm 1-P 6-M Logic CMOS Technology

4.0 mm x 8.0 mm

Object Recognition

200MHz @1.2V (Digital)

342 GOPS

534mW (Peak) / 320mW (Ave.)

9.6mJ/Frame

10.5nJ/Pixel

Aug. 2011 |

2011

WiPEA

Technology

Chip Size

Power Supply

Function

Life Time

Stimulation Current

Stimulation Freq.

Duty Cycle

Power Consumption

Released Date

0.13 μm 1P8M RF CMOS Technology

2.5mm x 5.0 mm (including pads)

1.2V

Multi-Modal Feedback EA Stimulation

> 1 hour

40μA ~ 1mA

1Hz ~ 500Hz

4% ~ 96%

6.8mW (@1mA EA stimulation)

Aug. 2011

|

2011

WiPEA

|

Technology

Chip Size

Power Supply

Function

Life Time

Stimulation Current

Stimulation Freq.

Duty Cycle

Power Consumption

Released Date |

0.13 μm 1P8M RF CMOS Technology

2.5mm x 5.0 mm (including pads)

1.2V

Multi-Modal Feedback EA Stimulation

> 1 hour

40μA ~ 1mA

1Hz ~ 500Hz

4% ~ 96%

6.8mW (@1mA EA stimulation)

Aug. 2011 |

2011

WHPlatform

Technology

Chip Size

Function

Power Supply

Operating Frequency

Power Consumption

Released Date

0.13 μm CMOS Technology

2.35 mm x 5.0 mm

Mental Health Monitoring System

1.2 V Battery Power

1 MHz

259.6 μw

Aug. 2011

|

2011

WHPlatform

|

Technology

Chip Size

Function

Power Supply

Operating Frequency

Power Consumption

Released Date |

0.13 μm CMOS Technology

2.35 mm x 5.0 mm

Mental Health Monitoring System

1.2 V Battery Power

1 MHz

259.6 μw

Aug. 2011 |

2010

IRIS

Technology

Chip Size

Operating Frequency

Peak Performance

Power Consumption

Released Date

0.13 μm 1-P 8-M Logic CMOS Technology

2.7 mm x 5 mm

200MHz @1.2V (Digital), 10MHz @1.0V (Analog)

49.14 GOPS

61mW

Aug. 2010

|

2010

IRIS

|

Technology

Chip Size

Operating Frequency

Peak Performance

Power Consumption

Released Date |

0.13 μm 1-P 8-M Logic CMOS Technology

2.7 mm x 5 mm

200MHz @1.2V (Digital), 10MHz @1.0V (Analog)

49.14 GOPS

61mW

Aug. 2010 |

2010

WiFAN-IV

Technology

Chip Size

Power Supply

Function

Clock Frequency

Energy Consumption

Power Consumption

Released Date

0.18 μm CMOS Technology

2.45mm x 2.6 mm(Network Controller), 2.45mm x 1.7mm(Sensor)

1.5V

ExG Sensing and Multi-Sensor Network Control

20MHz (TRX), 1.25MHz (Processor), 20kHz (Sensor)

0.33pJ/b

75μW (Network Controller), 25μW (Sensor)

Aug. 2010

|

2010

WiFAN-IV

|

Technology

Chip Size

Power Supply

Function

Clock Frequency

Energy Consumption

Power Consumption

Released Date |

0.18 μm CMOS Technology

2.45mm x 2.6 mm(Network Controller), 2.45mm x 1.7mm(Sensor)

1.5V

ExG Sensing and Multi-Sensor Network Control

20MHz (TRX), 1.25MHz (Processor), 20kHz (Sensor)

0.33pJ/b

75μW (Network Controller), 25μW (Sensor)

Aug. 2010 |

2010

Biocle IV

Technology

Chip Size

Function

Modulation

Sensitivity

Operating Frequency

Power Consumption

Released Date

0.18 μm CMOS Technology

2.5 mm x 5 mm

WBAN Transceiver

Double-FSK

-66dBm

40 - 120 MHz

2.4mW(RX), 2.0mW(TX)

Aug. 2010

|

2010

Biocle IV

|

Technology

Chip Size

Function

Modulation

Sensitivity

Operating Frequency

Power Consumption

Released Date |

0.18 μm CMOS Technology

2.5 mm x 5 mm

WBAN Transceiver

Double-FSK

-66dBm

40 - 120 MHz

2.4mW(RX), 2.0mW(TX)

Aug. 2010 |

2009

BONE-V4

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date

0.13 μm 1-P 8-M CMOS Technology

5 mm x 10 mm

Object Recognition

50~200MHz (PEs) / 400MHz (NoC)

1.2V

345mW

Aug. 2009

|

2009

BONE-V4

|

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date |

0.13 μm 1-P 8-M CMOS Technology

5 mm x 10 mm

Object Recognition

50~200MHz (PEs) / 400MHz (NoC)

1.2V

345mW

Aug. 2009 |

2009

SmartProbe

Technology

Chip Size

Function

Sensitivity

Injectable current

SNR

CMRR

Power Consumption

Released Date

0.18 μm CMOS Technology

5 mm x 5 mm

ECGs/Bio-Impedance monitoring sensor

3.17V/ohm for 0.1ohm

100uAp-p-250uAp-p (90kHz sinusoidal)

>40dB with input noise < 1mohm/srtHz

TIV=91dB, ECG=78dB

3.9mW for communication, 2.4mW for sensing

Aug. 2009

|

2009

SmartProbe

|

Technology

Chip Size

Function

Sensitivity

Injectable current

SNR

CMRR

Power Consumption

Released Date |

0.18 μm CMOS Technology

5 mm x 5 mm

ECGs/Bio-Impedance monitoring sensor

3.17V/ohm for 0.1ohm

100uAp-p-250uAp-p (90kHz sinusoidal)

>40dB with input noise < 1mohm/srtHz

TIV=91dB, ECG=78dB

3.9mW for communication, 2.4mW for sensing

Aug. 2009 |

2008

BONE-V3

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date

0.13 μm 1-P 8-M CMOS Technology

7 mm x 7 mm

Multiple Object Recognition

200MHz (IPs) / 400MHz (NoC)

1.2V

496mW

Sep. 2008

|

2008

BONE-V3

|

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date |

0.13 μm 1-P 8-M CMOS Technology

7 mm x 7 mm

Multiple Object Recognition

200MHz (IPs) / 400MHz (NoC)

1.2V

496mW

Sep. 2008 |

2008

Biocle III

Technology

Chip Size

Function

Sensitivity

Operating Frequency

Power Consumption

Released Date

0.18 μm CMOS Technology

1.9 mm x 2.5 mm

BCC/ MICS Dual-Band Transceiver

-65dBm(BCC), 35 μVrms(MICS)

30 - 70 MHz(BCC), 402- 405 MHz(MICS)

10.8mW(RX), 4.9mW(TX)

Aug. 2008

|

2008

Biocle III

|

Technology

Chip Size

Function

Sensitivity

Operating Frequency

Power Consumption

Released Date |

0.18 μm CMOS Technology

1.9 mm x 2.5 mm

BCC/ MICS Dual-Band Transceiver

-65dBm(BCC), 35 μVrms(MICS)

30 - 70 MHz(BCC), 402- 405 MHz(MICS)

10.8mW(RX), 4.9mW(TX)

Aug. 2008 |

2008

WiFAN-II

Technology

Chip Size

Power Supply

Operating Frequency

Rectifier Type

Rectifier Efficiency

Modulation

Power Consumption

Released Date

0.18 μm 1-P 6-M CMOS Logic Process

5 mm x 3 mm (Network Controller), 2.4 mm x 2 mm (Sensor)

1.8V

13.56 MHz(TX/HF) 402-405MHz(TX/MICS)

4-stage ATR CMOS

54.9% (HF), 45.2%(MICS)

15 % or 100 & ASK

5.2 mW (Network Controller), 12 μw(Sensor)

Aug. 2008

|

2008

WiFAN-II

|

Technology

Chip Size

Power Supply

Operating Frequency

Rectifier Type

Rectifier Efficiency

Modulation

Power Consumption

Released Date |

0.18 μm 1-P 6-M CMOS Logic Process

5 mm x 3 mm (Network Controller), 2.4 mm x 2 mm (Sensor)

1.8V

13.56 MHz(TX/HF) 402-405MHz(TX/MICS)

4-stage ATR CMOS

54.9% (HF), 45.2%(MICS)

15 % or 100 & ASK

5.2 mW (Network Controller), 12 μw(Sensor)

Aug. 2008 |

2007

BONE-V2

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date

0.13 μmSMIC 1-P 8-M CMOS Technology

6mm x 6mm

Object Recognition

200MHz (IPs) / 400MHz (NoC)

1.2V

583mW

Sep. 2007

|

2007

BONE-V2

|

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date |

0.13 μmSMIC 1-P 8-M CMOS Technology

6mm x 6mm

Object Recognition

200MHz (IPs) / 400MHz (NoC)

1.2V

583mW

Sep. 2007 |

2007

Biocle II

Technology

Chip Size

Function

Sensitivity

Operating Frequency

Power Supply

Power Consumption

Released Date

0.18 μm CMOS Technology

2 mm x 1.1 mm

Interference-Resilient Transceiver for Body Channel Communication

-65dBm

30 - 120 MHz

1.0/1.5 V

3.7mW

Aug. 2007

|

2007

Biocle II

|

Technology

Chip Size

Function

Sensitivity

Operating Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm CMOS Technology

2 mm x 1.1 mm

Interference-Resilient Transceiver for Body Channel Communication

-65dBm

30 - 120 MHz

1.0/1.5 V

3.7mW

Aug. 2007 |

2007

VitaComp-II

Technology

Chip Size

Power Supply

Operating Frequency

Latency Throughput

Transmission Rate

Sampling Rate

Power Consumption

Released Date

0.25 μm 1P 5M CMOS Logic Process

3 mm x 5 mm

2V

1 MHz

3-cycle, 1-cycle

1-8 Mb/s

0.1 - 1000 Samples/s

1.12 mW

Aug. 2007

|

2007

VitaComp-II

|

Technology

Chip Size

Power Supply

Operating Frequency

Latency Throughput

Transmission Rate

Sampling Rate

Power Consumption

Released Date |

0.25 μm 1P 5M CMOS Logic Process

3 mm x 5 mm

2V

1 MHz

3-cycle, 1-cycle

1-8 Mb/s

0.1 - 1000 Samples/s

1.12 mW

Aug. 2007 |

2007

WiFAN

Technology

Chip Size

Power Supply

Operating Frequency

Processing Speed

Gate Counts

Power Consumption

Functions

Released Date

TSMC 0.25um 1P5M CMOS Technology

1560um x 1280um (Including Pads)

2.5V

10MHz

10MHz

N/A

2.87mW

Fabric Area Network Controller

Jun. 2007

|

2007

WiFAN

|

Technology

Chip Size

Power Supply

Operating Frequency

Processing Speed

Gate Counts

Power Consumption

Functions

Released Date |

TSMC 0.25um 1P5M CMOS Technology

1560um x 1280um (Including Pads)

2.5V

10MHz

10MHz

N/A

2.87mW

Fabric Area Network Controller

Jun. 2007 |

2006

Biocle, Clearphone

Technology

Area

Power supply

Frequency

Gate Counts

Power consumption

Functions

Released Date

0.18 μm TSMC 1-P 6-M CMOS Technology

7.7mm x 5mm

1.8V

400 MHz (NoC) / 200 MHz (Other Part)

838.8K Gates (NAND2 Equiv.)

1.4W (Peak)

Vision Recognition

Dec. 2006

|

2006

Biocle, Clearphone

|

Technology

Area

Power supply

Frequency

Gate Counts

Power consumption

Functions

Released Date |

0.18 μm TSMC 1-P 6-M CMOS Technology

7.7mm x 5mm

1.8V

400 MHz (NoC) / 200 MHz (Other Part)

838.8K Gates (NAND2 Equiv.)

1.4W (Peak)

Vision Recognition

Dec. 2006 |

2006

RamP-VI

Technology

Area

Power supply

Frequency

Transistors

Processing speed

Power management

Power consumption

Functions

Released Date

0.18 μm TSMC 1-P 6-M CMOS Technology

Core: 17.2mm2 , Die: 25mm2

Core: 1.0V - 1.8V, I/O: 3.3V

89MHz - 200MHz

1.57Mtransistors, 29KB SRAM

141Mvertices/s, 50Mpixels/s

Triple power domains with DVFS

52.4mW @ 60fps

OpenGL-ES 2.0

Sep. 2006

|

2006

RamP-VI

|

Technology

Area

Power supply

Frequency

Transistors

Processing speed

Power management

Power consumption

Functions

Released Date |

0.18 μm TSMC 1-P 6-M CMOS Technology

Core: 17.2mm2 , Die: 25mm2

Core: 1.0V - 1.8V, I/O: 3.3V

89MHz - 200MHz

1.57Mtransistors, 29KB SRAM

141Mvertices/s, 50Mpixels/s

Triple power domains with DVFS

52.4mW @ 60fps

OpenGL-ES 2.0

Sep. 2006 |

2006

Clearphone+

Technology

Area

Power supply

Frequency

Power consumption

Functions

Released Date

0.18 μm TSMC 1-P 6-M CMOS Technology

3.74mm2

0.9V

32kHz

108 μW

Digital hearing aid with ear modeling filter

Sep. 2006

|

2006

Clearphone+

|

Technology

Area

Power supply

Frequency

Power consumption

Functions

Released Date |

0.18 μm TSMC 1-P 6-M CMOS Technology

3.74mm2

0.9V

32kHz

108 μW

Digital hearing aid with ear modeling filter

Sep. 2006 |

2006

μ-RamP

Technology

Area

Power supply

Frequency

Capacity

Operation Mode

Date Rate

Power consumption

Latency

Released Date

90nm, diode-switch PRAM, 3-metal CMOS

3,085μm x 1,940μm

1.8V

100MHz

4Mb ( 256k x 16 bit )

SM : Single access mode

BM : Burst access mode

SDM : Setup and debug mode

RM : RISC Operation mode

100Mb/s/pin read and write ( in BM )

SM: 21.6mW BM: 28.4 mW

SM…

|

2006

μ-RamP

|

Technology

Area

Power supply

Frequency

Capacity

Operation Mode

Date Rate

Power consumption

Latency

Released Date |

90nm, diode-switch PRAM, 3-metal CMOS

3,085μm x 1,940μm

1.8V

100MHz

4Mb ( 256k x 16 bit )

SM : Single access mode

BM : Burst access mode

SDM : Setup and debug mode

RM : RISC Operation mode

100Mb/s/pin read and write ( in BM )

SM: 21.6mW BM: 28.4 mW

SM… |

2005

Biocle, Clearphone

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

Body-Coupled PHY Transceiver, Digital Hearing Aid

160MHz, 32kHz

0.9V, 0.9V

2.6mW, 96μW

Dec. 2005

|

2005

Biocle, Clearphone

|

Technology

Chip Size

Function

Operating Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

Body-Coupled PHY Transceiver, Digital Hearing Aid

160MHz, 32kHz

0.9V, 0.9V

2.6mW, 96μW

Dec. 2005 |

2005

BioMAP

Technology

Chip Size

Function

Memory

Operating Frequency

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

Body Sensor Network management

768 Kb SRAM

4.2MHz for system bus, 8.192~32.768kHz for Sensor Management

0.6 V core, 0.6 V-1.8 V peripheral

24.2 μW avg

Dec. 2005

|

2005

BioMAP

|

Technology

Chip Size

Function

Memory

Operating Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

Body Sensor Network management

768 Kb SRAM

4.2MHz for system bus, 8.192~32.768kHz for Sensor Management

0.6 V core, 0.6 V-1.8 V peripheral

24.2 μW avg

Dec. 2005 |

2005

Logarithm Arithmetic Unit (LAU)

Technology

Chip Size

Gate Count

Function

Operating Frequency

Latency/Throughput

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

1 mm x 1 mm (core) / 4 mm x 4 mm (die, pad limited)

9 K

Logarithmic Arithmetic Unit

213 MHz

2-cycle/1-cycle

1.8 V

2.18 mW (1-operand) / 3.07 mW (2-operand)

Mar. 2005

|

2005

Logarithm Arithmetic Unit (LAU)

|

Technology

Chip Size

Gate Count

Function

Operating Frequency

Latency/Throughput

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

1 mm x 1 mm (core) / 4 mm x 4 mm (die, pad limited)

9 K

Logarithmic Arithmetic Unit

213 MHz

2-cycle/1-cycle

1.8 V

2.18 mW (1-operand) / 3.07 mW (2-operand)

Mar. 2005 |

2005

RamP-C2

Technology

Chip Size

Gate Count

Function

Clock Frequency

Pixel Fill Rate

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

330 KGate+164 Kb embedded SRAM

- Gouraud Shading

- Texture Mapping / Blending

- Pixel Alpha Blending

10 MHz

20 Mpixels/s

1.8 V (Core) / 3.3 V (I/O)

< 17.2 mW

Mar. 2005

|

2005

RamP-C2

|

Technology

Chip Size

Gate Count

Function

Clock Frequency

Pixel Fill Rate

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

330 KGate+164 Kb embedded SRAM

- Gouraud Shading

- Texture Mapping / Blending

- Pixel Alpha Blending

10 MHz

20 Mpixels/s

1.8 V (Core) / 3.3 V (I/O)

< 17.2 mW

Mar. 2005 |

2005

Body Channel Tester, RFID+Sensor, Bandgap Reference

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

2 mm x 2 mm

- Human Body Communication

- Pixel Alpha Blending

- RF Powered Sensors(Temperature and Photo Sensor)

- 1MHz (Body Channel Communication)

- 40KHz (RFID+Sensor)

- N/A (Bandgap Reference)

1 V/ 1.5-2.5 V / N/A

250 μ W/ 5 μ W / N/A

…

|

2005

Body Channel Tester, RFID+Sensor, Bandgap Reference

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

2 mm x 2 mm

- Human Body Communication

- Pixel Alpha Blending

- RF Powered Sensors(Temperature and Photo Sensor)

- 1MHz (Body Channel Communication)

- 40KHz (RFID+Sensor)

- N/A (Bandgap Reference)

1 V/ 1.5-2.5 V / N/A

250 μ W/ 5 μ W / N/A

… |

2004

RamP-Lite

Technology

Chip Size

Gate Count

Function

Clock Frequency

Pixel Fill Rate

Power Supply

Power Consumption

Pin Package

Released Date

Samsung 0.18 μm 1-poly 6-metal CMOS Technology

5 mm x 5 mm (Core: 1.59 mm x 1.59 mm)

181 K

- Lighting

- Triangle Setup

- Gouraud Shading

- Texture Mapping

- Alpha Blending

20 MHz

20 Mpixels/s

1.8 V (Core) / 3.3 V (I/O)

14.7 mW

208 pin QFP

Oct. 2004…

|

2004

RamP-Lite

|

Technology

Chip Size

Gate Count

Function

Clock Frequency

Pixel Fill Rate

Power Supply

Power Consumption

Pin Package

Released Date |

Samsung 0.18 μm 1-poly 6-metal CMOS Technology

5 mm x 5 mm (Core: 1.59 mm x 1.59 mm)

181 K

- Lighting

- Triangle Setup

- Gouraud Shading

- Texture Mapping

- Alpha Blending

20 MHz

20 Mpixels/s

1.8 V (Core) / 3.3 V (I/O)

14.7 mW

208 pin QFP

Oct. 2004… |

2004

Preamplifier, PLL, Sigma-Delta Modulator

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm DongbuAnam CMOS Technology

2 mm x 2 mm

- Automatic Gain Control Preamplifier with Exponential Gain Control

- PLL

- Sigma-Delta Modulator

N/A (Preamplifier) / 2 GHz (PLL) / 1/2 MHz (Modulator)

1.1 V / 2.0 V / 0.9 V

40 μ W

Sep. 2004

|

2004

Preamplifier, PLL, Sigma-Delta Modulator

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm DongbuAnam CMOS Technology

2 mm x 2 mm

- Automatic Gain Control Preamplifier with Exponential Gain Control

- PLL

- Sigma-Delta Modulator

N/A (Preamplifier) / 2 GHz (PLL) / 1/2 MHz (Modulator)

1.1 V / 2.0 V / 0.9 V

40 μ W

Sep. 2004 |

2004

RamP-V

Technology

Chip Size

Power Supply

Operating Frequency

Processing Speed

GateCounts

Transistors

Power Consumption

Functions

Released Date

0.18 μm 1P 6M CMOS Logic Process

6 mm x6 mm

3.3V (I/O), 1.8V(Core)

200 MHz

50M Verticles/s, 50Mpixel/s (Bilinear Texture Filtering)

2M Logic Gates

96kB SRAM

< 155mW

Fixed-Point Programmable Vertex Shader

Sep. 2004

|

2004

RamP-V

|

Technology

Chip Size

Power Supply

Operating Frequency

Processing Speed

GateCounts

Transistors

Power Consumption

Functions

Released Date |

0.18 μm 1P 6M CMOS Logic Process

6 mm x6 mm

3.3V (I/O), 1.8V(Core)

200 MHz

50M Verticles/s, 50Mpixel/s (Bilinear Texture Filtering)

2M Logic Gates

96kB SRAM

< 155mW

Fixed-Point Programmable Vertex Shader

Sep. 2004 |

2004

Autonomous SRAM with SAC Scheme

Technology

Chip Size

Density

Function

Power Supply

Released Date

Samsung 80 nm Double-Stacked Cell Technology

1152 μ m x 1728 μ m

512 Kb

- Sensing Internal Status of SRAM

- Analyzing the Data and Control Internal Parameters

1.6 V (Internal) / 3.3 V (External)

Aug. 2004

|

2004

Autonomous SRAM with SAC Scheme

|

Technology

Chip Size

Density

Function

Power Supply

Released Date |

Samsung 80 nm Double-Stacked Cell Technology

1152 μ m x 1728 μ m

512 Kb

- Sensing Internal Status of SRAM

- Analyzing the Data and Control Internal Parameters

1.6 V (Internal) / 3.3 V (External)

Aug. 2004 |

2004

Network-on-Chip with High-speed Serial Links

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

- A Network-on-Chip with 3Gbps/wire Serialized On-chip

Interconnect Using Adaptive Control Schemes

400MHz input, 1.6 ~ 3.0 Gb/s/wire operation

1.8V (core), 3.3V (I/O)

N/A

May. 2004

|

2004

Network-on-Chip with High-speed Serial Links

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

- A Network-on-Chip with 3Gbps/wire Serialized On-chip

Interconnect Using Adaptive Control Schemes

400MHz input, 1.6 ~ 3.0 Gb/s/wire operation

1.8V (core), 3.3V (I/O)

N/A

May. 2004 |

2003

Analog Front-End for USB-OTG

Technology

Chip Size

Function

Clock Frequency

Power Supply

Output Voltage

Power Efficiency

Load Current

Released Date

0.13 μm Samsung 3.3 V CMOS Technology

0.5 mm x 0.5 mm

Analog Front-End Compatible with USB On-The-Go

500KHz

3.3 V

5.0 V

> 70 %

> 30 mA

Oct. 2003

|

2003

Analog Front-End for USB-OTG

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Output Voltage

Power Efficiency

Load Current

Released Date |

0.13 μm Samsung 3.3 V CMOS Technology

0.5 mm x 0.5 mm

Analog Front-End Compatible with USB On-The-Go

500KHz

3.3 V

5.0 V

> 70 %

> 30 mA

Oct. 2003 |

2003

An 800MHz Star-Connected On-Chip Network

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.18 μm DongnuAnam CMOS Technology

5 mm x 5 mm

Multimedia SoC with Low-Power On-Chip Network

1.6 GHz for On-Chip Network

100 MHz for Processors

1.8 V (core), 3.3 V (I/O), 0.6 V (Small-swing-Interconnection)

On-Chip Network < 51 mW

Sep. 2003

|

2003

An 800MHz Star-Connected On-Chip Network

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm DongnuAnam CMOS Technology

5 mm x 5 mm

Multimedia SoC with Low-Power On-Chip Network

1.6 GHz for On-Chip Network

100 MHz for Processors

1.8 V (core), 3.3 V (I/O), 0.6 V (Small-swing-Interconnection)

On-Chip Network < 51 mW

Sep. 2003 |

2003

CAMi

Technology

Chip Size

Function

Memory Capacity

Power Supply

Search Time

Energy Efficiency

Released Date

0.10 μm Samsung CMOS Process Technology

4.2 mm x 2.8 mm

- Low Power CAM Architecture Including

- Hidden Bank Selection Scheme

- Match Line Repeater

- Sub Match Line

- Column Decoding

144 Kb

1.2 V

2.2 ns

0.7 fJ/bit/search

Aug. 2003

|

2003

CAMi

|

Technology

Chip Size

Function

Memory Capacity

Power Supply

Search Time

Energy Efficiency

Released Date |

0.10 μm Samsung CMOS Process Technology

4.2 mm x 2.8 mm

- Low Power CAM Architecture Including

- Hidden Bank Selection Scheme

- Match Line Repeater

- Sub Match Line

- Column Decoding

144 Kb

1.2 V

2.2 ns

0.7 fJ/bit/search

Aug. 2003 |

2002

Motion Express

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date

0.16 μm Hynix CMOS DRAM Technology

6 mm x 6 mm

A MPEG

- 4 acceleration IP for Portable Video Application

27 MHz

~10,000

2.5 V(core), 3.3 V(I/O)

< 6 mW

Oct. 2002

|

2002

Motion Express

|

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date |

0.16 μm Hynix CMOS DRAM Technology

6 mm x 6 mm

A MPEG

- 4 acceleration IP for Portable Video Application

27 MHz

~10,000

2.5 V(core), 3.3 V(I/O)

< 6 mW

Oct. 2002 |

2002

RamP- IV

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date

0.16 μm Hynix CMOS DRAM Technology

6 mm x 6 mm

- 3D Graphic Processor for Mobile Application

- 132/33 MHz for FAST mode

66/16.5 MHz for NORMAL mode

33/8.25 MHz for SLOW mode

60,000,000

2.3 V

210 mW

Oct. 2002

|

2002

RamP- IV

|

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date |

0.16 μm Hynix CMOS DRAM Technology

6 mm x 6 mm

- 3D Graphic Processor for Mobile Application

- 132/33 MHz for FAST mode

66/16.5 MHz for NORMAL mode

33/8.25 MHz for SLOW mode

60,000,000

2.3 V

210 mW

Oct. 2002 |

2002

An 800MHz Star-Connected On-Chip Network

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date

0.16 μm DRAM Technology with 3 AI

10.8 mm x 6.0 mm

- On-chip packet transaction with plesiochronous communication

- Off-chip packet transaction for scalability

core @ 800 MHz

IP Block @ 200 MHz

81,000 (without 1 Kb SRAM)

2.3 V

264 mW

Oct. 2002

|

2002

An 800MHz Star-Connected On-Chip Network

|

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date |

0.16 μm DRAM Technology with 3 AI

10.8 mm x 6.0 mm

- On-chip packet transaction with plesiochronous communication

- Off-chip packet transaction for scalability

core @ 800 MHz

IP Block @ 200 MHz

81,000 (without 1 Kb SRAM)

2.3 V

264 mW

Oct. 2002 |

2002

10 Gbps/port 8x8 Shared-bus Switch Fabric

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date

0.16 μm DRAM Technology with 3 AI

4 mm x 9 mm

10 Gbps/port 8x8 Shared-bus witch fabric with Hierarchical Output

Buffer

200 MHz for Dual port SRAM

20 MHz for Embedded DRAM (w/ 512 bits I/O)

32 Kb SRAM, 1 Mb DRAM

2.3 V

240 mW

Oct. 2002

|

2002

10 Gbps/port 8x8 Shared-bus Switch Fabric

|

Technology

Chip Size

Function

Clock Frequency

Transistor Counts

Power Supply

Power Consumption

Released Date |

0.16 μm DRAM Technology with 3 AI

4 mm x 9 mm

10 Gbps/port 8x8 Shared-bus witch fabric with Hierarchical Output

Buffer

200 MHz for Dual port SRAM

20 MHz for Embedded DRAM (w/ 512 bits I/O)

32 Kb SRAM, 1 Mb DRAM

2.3 V

240 mW

Oct. 2002 |

2001

Fully Differential CMOS TIA

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm Anam CMOS & Telephus Multichip-on-Oxide Process

Technology

5 mm x 5 mm

0.13 mm x 0.16 mm

250 μ m x 350 μ m

Transimpedance amplifier

N/A

2.5 V

27 mW @ 1 Gb/s

Aug. 2001

|

2001

Fully Differential CMOS TIA

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm Anam CMOS & Telephus Multichip-on-Oxide Process

Technology

5 mm x 5 mm

0.13 mm x 0.16 mm

250 μ m x 350 μ m

Transimpedance amplifier

N/A

2.5 V

27 mW @ 1 Gb/s

Aug. 2001 |

2001

MPTC

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.16 μm HynixCMOS DRAM Technology

15.6 mm x 7.5 mm

Multilevel Parallel Texture Cache

150 MHz

2.5 V

89 mW

May. 2001

|

2001

MPTC

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.16 μm HynixCMOS DRAM Technology

15.6 mm x 7.5 mm

Multilevel Parallel Texture Cache

150 MHz

2.5 V

89 mW

May. 2001 |

2001

4Gb/s CDR

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm Dongbu CMOS Technology

0.9 mm x 1.0 mm

4-Gb/s Clock and Data Recovery(CDR)

Circuit performing 1:4 DEMUX

500 MHz

2.5 V

70 mW

May. 2001

|

2001

4Gb/s CDR

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm Dongbu CMOS Technology

0.9 mm x 1.0 mm

4-Gb/s Clock and Data Recovery(CDR)

Circuit performing 1:4 DEMUX

500 MHz

2.5 V

70 mW

May. 2001 |

2000

2Gb/s CDR

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm Anam CMOS Technology

1.0 mm x 2.0 mm

2-Gb/s Clock and Data Recovery(CDR)

Circuit performing 1:2 DEMUX

1 GHz

2.5 V

100 mW

Dec. 2000

|

2000

2Gb/s CDR

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm Anam CMOS Technology

1.0 mm x 2.0 mm

2-Gb/s Clock and Data Recovery(CDR)

Circuit performing 1:2 DEMUX

1 GHz

2.5 V

100 mW

Dec. 2000 |

2000

RamP-II

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.18 μm Hynix CMOS EML Technology

84 mm2

One-Chip PDA Solution

20/80/100 MHz

1.8/2.5 V

160 mW

Jul. 2000

|

2000

RamP-II

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm Hynix CMOS EML Technology

84 mm2

One-Chip PDA Solution

20/80/100 MHz

1.8/2.5 V

160 mW

Jul. 2000 |

2000

2.5Gb/s LVDS Transmitter

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm Anam CMOS Technology

2.0 mm x 2.0 mm

2.5 Gb/s LVDS Transmitter for optical interconnections

N/A

2.5 V

50 mW

Feb. 2000

|

2000

2.5Gb/s LVDS Transmitter

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm Anam CMOS Technology

2.0 mm x 2.0 mm

2.5 Gb/s LVDS Transmitter for optical interconnections

N/A

2.5 V

50 mW

Feb. 2000 |

2000

1.3Gb/s LVDS Receiver

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm Anam CMOS Technology

2.0 mm x 2.0 mm

1.3 Gb/s LVDS receiver for optical interconnections

N/A

2.5 V

51 mW

Feb. 2000

|

2000

1.3Gb/s LVDS Receiver

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm Anam CMOS Technology

2.0 mm x 2.0 mm

1.3 Gb/s LVDS receiver for optical interconnections

N/A

2.5 V

51 mW

Feb. 2000 |

1999

Ultra Fast 64bit Adder

Technology Chip Size Function Clock Frequency Power Supply Power Consumption Released Date

0.25 μm Anam CMOS Technology

1.4 mm x 0.6 mm

Dynamic 64bit Adder

N/A

2.5 V

100 mW @ 500 MHz

Dec. 1999

|

1999

Ultra Fast 64bit Adder

|

Technology Chip Size Function Clock Frequency Power Supply Power Consumption Released Date |

0.25 μm Anam CMOS Technology

1.4 mm x 0.6 mm

Dynamic 64bit Adder

N/A

2.5 V

100 mW @ 500 MHz

Dec. 1999 |

1999

Ultra Fast 64bit Adder

Technology Chip Size Function Clock Frequency Power Supply Power Consumption Released Date

0.25 μm Anam CMOS Technology 0.8 mm x 0.15 mm High-speed 64bit Adder with carry in/out 1 GHz 2.5 V N/A Dec. 1999

|

1999

Ultra Fast 64bit Adder

|

Technology Chip Size Function Clock Frequency Power Supply Power Consumption Released Date |

0.25 μm Anam CMOS Technology 0.8 mm x 0.15 mm High-speed 64bit Adder with carry in/out 1 GHz 2.5 V N/A Dec. 1999 |

1999

RamP-I

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.35 μm Hynix CMOS DRAM Technology

56 mm2

EML 3D- Rendering Engine

100 MHz

3.3 V

590 mW

Aug. 1999

|

1999

RamP-I

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.35 μm Hynix CMOS DRAM Technology

56 mm2

EML 3D- Rendering Engine

100 MHz

3.3 V

590 mW

Aug. 1999 |