2004

RamP-Lite

Technology

Chip Size

Gate Count

Function

Clock Frequency

Pixel Fill Rate

Power Supply

Power Consumption

Pin Package

Released Date

Samsung 0.18 μm 1-poly 6-metal CMOS Technology

5 mm x 5 mm (Core: 1.59 mm x 1.59 mm)

181 K

- Lighting

- Triangle Setup

- Gouraud Shading

- Texture Mapping

- Alpha Blending

20 MHz

20 Mpixels/s

1.8 V (Core) / 3.3 V (I/O)

14.7 mW

208 pin QFP

Oct. 2004…

|

2004

RamP-Lite

|

Technology

Chip Size

Gate Count

Function

Clock Frequency

Pixel Fill Rate

Power Supply

Power Consumption

Pin Package

Released Date |

Samsung 0.18 μm 1-poly 6-metal CMOS Technology

5 mm x 5 mm (Core: 1.59 mm x 1.59 mm)

181 K

- Lighting

- Triangle Setup

- Gouraud Shading

- Texture Mapping

- Alpha Blending

20 MHz

20 Mpixels/s

1.8 V (Core) / 3.3 V (I/O)

14.7 mW

208 pin QFP

Oct. 2004… |

2004

Preamplifier, PLL, Sigma-Delta Modulator

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.25 μm DongbuAnam CMOS Technology

2 mm x 2 mm

- Automatic Gain Control Preamplifier with Exponential Gain Control

- PLL

- Sigma-Delta Modulator

N/A (Preamplifier) / 2 GHz (PLL) / 1/2 MHz (Modulator)

1.1 V / 2.0 V / 0.9 V

40 μ W

Sep. 2004

|

2004

Preamplifier, PLL, Sigma-Delta Modulator

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.25 μm DongbuAnam CMOS Technology

2 mm x 2 mm

- Automatic Gain Control Preamplifier with Exponential Gain Control

- PLL

- Sigma-Delta Modulator

N/A (Preamplifier) / 2 GHz (PLL) / 1/2 MHz (Modulator)

1.1 V / 2.0 V / 0.9 V

40 μ W

Sep. 2004 |

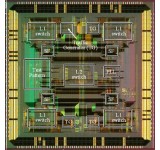

2004

RamP-V

Technology

Chip Size

Power Supply

Operating Frequency

Processing Speed

GateCounts

Transistors

Power Consumption

Functions

Released Date

0.18 μm 1P 6M CMOS Logic Process

6 mm x6 mm

3.3V (I/O), 1.8V(Core)

200 MHz

50M Verticles/s, 50Mpixel/s (Bilinear Texture Filtering)

2M Logic Gates

96kB SRAM

< 155mW

Fixed-Point Programmable Vertex Shader

Sep. 2004

|

2004

RamP-V

|

Technology

Chip Size

Power Supply

Operating Frequency

Processing Speed

GateCounts

Transistors

Power Consumption

Functions

Released Date |

0.18 μm 1P 6M CMOS Logic Process

6 mm x6 mm

3.3V (I/O), 1.8V(Core)

200 MHz

50M Verticles/s, 50Mpixel/s (Bilinear Texture Filtering)

2M Logic Gates

96kB SRAM

< 155mW

Fixed-Point Programmable Vertex Shader

Sep. 2004 |

2004

Autonomous SRAM with SAC Scheme

Technology

Chip Size

Density

Function

Power Supply

Released Date

Samsung 80 nm Double-Stacked Cell Technology

1152 μ m x 1728 μ m

512 Kb

- Sensing Internal Status of SRAM

- Analyzing the Data and Control Internal Parameters

1.6 V (Internal) / 3.3 V (External)

Aug. 2004

|

2004

Autonomous SRAM with SAC Scheme

|

Technology

Chip Size

Density

Function

Power Supply

Released Date |

Samsung 80 nm Double-Stacked Cell Technology

1152 μ m x 1728 μ m

512 Kb

- Sensing Internal Status of SRAM

- Analyzing the Data and Control Internal Parameters

1.6 V (Internal) / 3.3 V (External)

Aug. 2004 |

2004

Network-on-Chip with High-speed Serial Links

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

- A Network-on-Chip with 3Gbps/wire Serialized On-chip

Interconnect Using Adaptive Control Schemes

400MHz input, 1.6 ~ 3.0 Gb/s/wire operation

1.8V (core), 3.3V (I/O)

N/A

May. 2004

|

2004

Network-on-Chip with High-speed Serial Links

|

Technology

Chip Size

Function

Clock Frequency

Power Supply

Power Consumption

Released Date |

0.18 μm DongbuAnam CMOS Technology

5 mm x 5 mm

- A Network-on-Chip with 3Gbps/wire Serialized On-chip

Interconnect Using Adaptive Control Schemes

400MHz input, 1.6 ~ 3.0 Gb/s/wire operation

1.8V (core), 3.3V (I/O)

N/A

May. 2004 |